Versuch 1

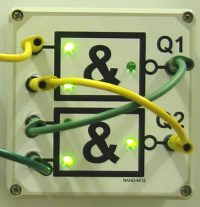

Set-Reset (RS) Flipflop mit zwei NAND-Gattern. Das Flipflop wird gesetzt (Q=1) durch einen Übergang 1 --> 0 am jeweiligen Eingang.

Set-Reset (RS) Flipflop mit zwei NAND-Gattern. Das Flipflop wird gesetzt (Q=1) durch einen Übergang 1 --> 0 am jeweiligen Eingang.

Versuch 2

Set-Reset (RS) Flipflop mit zwei NOR-Gattern. Das Flipflop wird gesetzt (Q=1) durch einen Übergang 0 --> 1 am jeweiligen Eingang.

Set-Reset (RS) Flipflop mit zwei NOR-Gattern. Das Flipflop wird gesetzt (Q=1) durch einen Übergang 0 --> 1 am jeweiligen Eingang.

Versuch 3

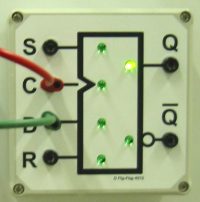

Data-Flipflop (D-Flipflop). Der logische Wert am D-Eingang wird mit der steigenden Flanke des Clock-Impulses übernommen und bleibt dort bis zur nächsten steigenden Clock-Flanke erhalten. Diese Schaltung "verriegelt" einen Datenwert (engl.: latch). Mit den Eingängen R (=Reset) und S (=Set) kann das Flipflop zwangsweise in die Zustände Q=0 und Q=1 gebracht werden.

Data-Flipflop (D-Flipflop). Der logische Wert am D-Eingang wird mit der steigenden Flanke des Clock-Impulses übernommen und bleibt dort bis zur nächsten steigenden Clock-Flanke erhalten. Diese Schaltung "verriegelt" einen Datenwert (engl.: latch). Mit den Eingängen R (=Reset) und S (=Set) kann das Flipflop zwangsweise in die Zustände Q=0 und Q=1 gebracht werden.

Versuch 4

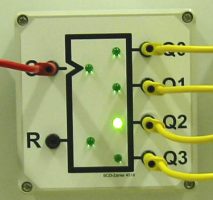

BCD-Zähler mit 7-Segment Dekoder. Der Zähler wird durch eine positive Flanke am Clock-Input inkrementiert. Beim Erreichen des Zählerstandes 9 springt er auf 0 zurück. Mit dem Reseteingang kann der Zähler auch asynchron auf 0 gestellt werden.

BCD-Zähler mit 7-Segment Dekoder. Der Zähler wird durch eine positive Flanke am Clock-Input inkrementiert. Beim Erreichen des Zählerstandes 9 springt er auf 0 zurück. Mit dem Reseteingang kann der Zähler auch asynchron auf 0 gestellt werden.